It feels like it was just yesterday that Intel announced three new CPU families for its 9th Generation processors, and now the chipmaker is already talking about its next-generation 10nm microarchitecture.

Meet Sunny Cove, Intel’s next-generation 10nm CPU microarchitecture that will serve the basis of the company‘s new line of server (Xeon series) and client (Core series) CPUs due to arrive in the second half of 2019. As you might expect, Intel’s new microarchitecture promises the usual increases in performance per clock and power efficiency; however, Team Blue also plans to introduce new features to accelerate special purpose computing tasks, like AI and cryptography.

Sunny Cove will specifically have algorithms to reduce latency, while the enhanced microarchitecture will enable more computing operations to be executed in parallel. This should all translate into snappier performance from Intel’s next-gen chips as well as better multi-core performance.

On the data-centric side, Intel claims Sunny Cove will feature larger key buffers and memory caches to optimize workloads. While most of this boost in cryptography performance won’t matter to most consumers, these improvements should lead to faster file compression and decompression across the board on all Sunny Cove CPUs.

Intel even showed off a demo where a Sunny Cove CPU was able to perform a 7-Zip encode using AES-256 75% faster than an equivalent current Intel CPU. Of course, there was also the caveat of Intel using a recompiled version of 7-Zip designed to take advantage of Sunny Cove's instructions.

Unfortunately, there are still many more unanswered questions. Intel didn’t disclose any hard figures on what we can expect in terms of ‘frequency increases’ or talk about how many cores this microarchitecture will support. We’re sure to hear more about going into next year though.

Going 3D

The other big highlight for processors to come out of Intel’s Architecture Day was a new 3D packaging process that could revolutionize CPUs. Intel demonstrated a new 3D packaging technology called 'Foveros' that essentially allows Intel to stack graphics and even AI processors onto its CPUs.

Get the best Black Friday deals direct to your inbox, plus news, reviews, and more.

Sign up to be the first to know about unmissable Black Friday deals on top tech, plus get all your favorite TechRadar content.

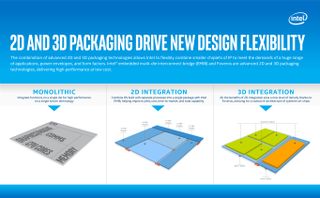

For the most part, Intel’s processors up to this point utilized either monolithic or 2D integration packaging. The former makes up the bulk of Intel’s processors, in which the CPU core, integrated memory, I/O and graphics are all integrated into a single die.

Intel recently introduced 2D integration with its Kaby Lake G processors, which essentially conjoins Intel CPU cores with discrete-class AMD graphics. Although the two separate components are built into a single package, they are only connected through the use of Embedded Multi-die Interconnect Bridge that enables high-speed communication.

Foveros is essentially an evolution of this 2D integration, in which other components can be stacked on top of each other in a form of logic-on-logic integration. Whereas Intel's previous EMIB technology utilized silicon bridges, Foveros introduces thousands of "microbumps" to create direct face-to-face connections between the stacked parts.

Intel’s first example of a Foveros product in action combines a high-performance 10nm compute-stacked chiplet with a low-power 22FFL base die. According to Intel, this specific combination will allow small form factor devices to deliver both performance and power efficiency at the same time.

This technology most immediately will enable greater flexibility and potentially lead to new form factors.

For example, the lack of memory and I/O has been a pain point of increasingly thin Ultrabooks, but this 3D packaging process may solve the problem. Instead of having to squeeze I/O, SRAM and power delivery circuits into a small flat plane, they could be all fabricated into the base die of a CPU with a full-sized high-performance logic chiplet stacked on top.

Ultimately, consider this Intel's method of keeping up with Moore's Law short of shrinking its die size further, which it's still hard at work on.

- We're hoping for some real evolution in the world of the best processors

Kevin Lee was a former computing reporter at TechRadar. Kevin is now the SEO Updates Editor at IGN based in New York. He handles all of the best of tech buying guides while also dipping his hand in the entertainment and games evergreen content. Kevin has over eight years of experience in the tech and games publications with previous bylines at Polygon, PC World, and more. Outside of work, Kevin is major movie buff of cult and bad films. He also regularly plays flight & space sim and racing games. IRL he's a fan of archery, axe throwing, and board games.